秉承“取之于开源,贡献于开源”的理念,进迭时空在 Debug 软件的开发与维护中,始终坚持 Upstream First 原则,积极将优化与修复反馈至开源上游,与全球开发者共同推动 RISC-V 生态的繁荣与发展。

RISC-V 调试所涉及的核心开源软件主要包括 GDB 和 OpenOCD。

目前,riscv-openocd 已实现对 RISC-V 调试规范 v0.11 和 v0.13 的支持,并部分集成 v1.0 特性,能够满足日常开发调试需求,且仍在持续演进中。

此外,riscv-test 项目(https://github.com/riscv-software-src/riscv-tests )中提供了一套 Debug Tests 测试套件。由于调试过程依赖于多个系统组件的协同工作,该测试套件通过 Python 脚本调用 OpenOCD 和 GDB,模拟真实调试流程,执行端到端测试,从而有助于发现从Debug接口到相关底层组件中可能存在的问题。

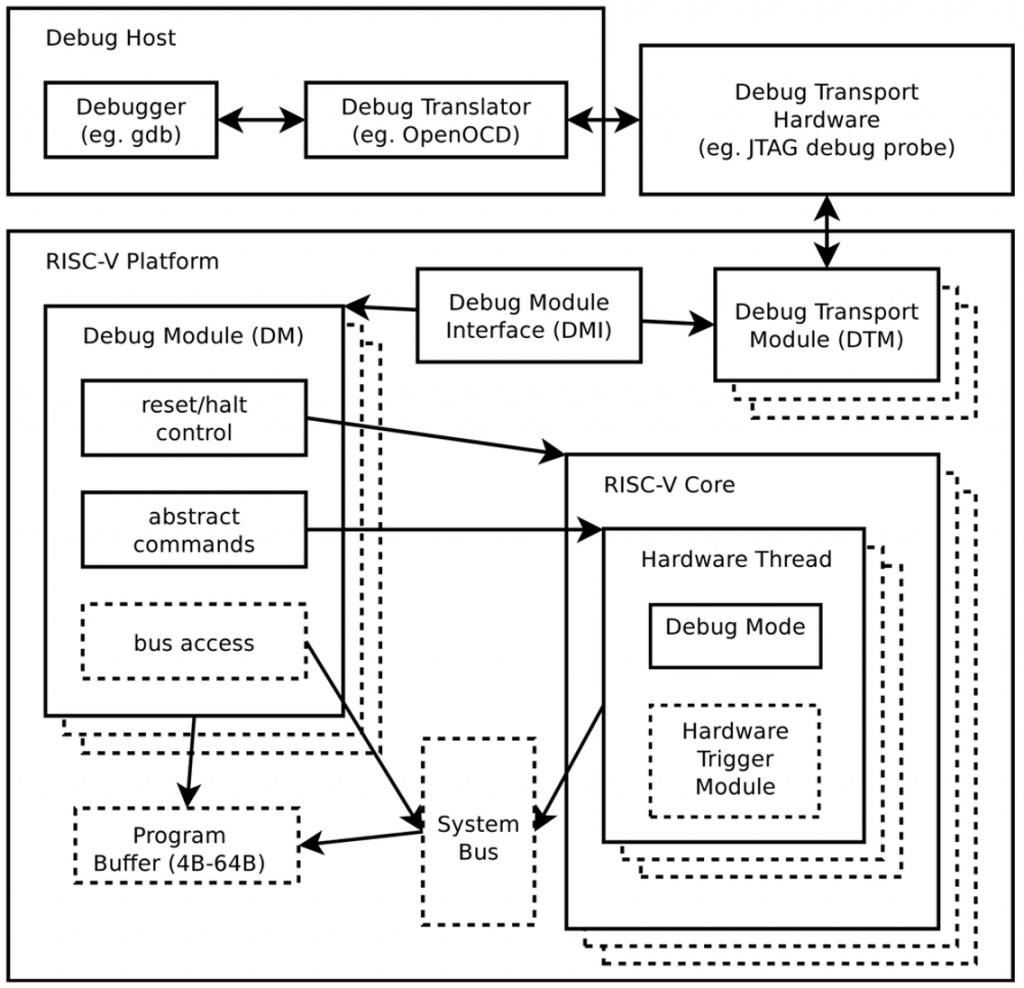

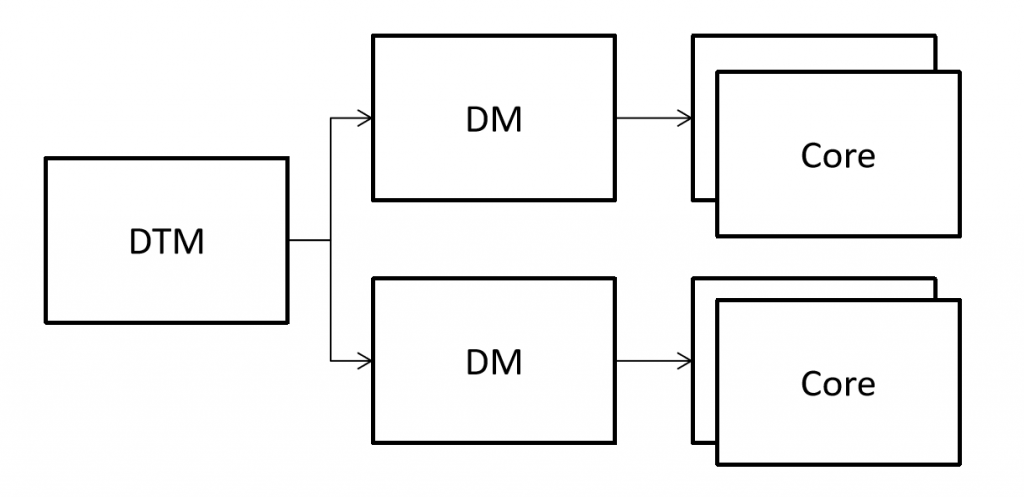

在进迭时空首款 RISC-V AI CPU K1 芯片的研发过程中,OpenOCD 与 riscv-tests 在调试验证环节发挥了关键作用。在 K1 研发阶段,OpenOCD 已具备较为完善的基础调试功能,然而,由于 K1 的硬件架构将 8 个核心分为 2 个Cluster,每个Cluster对应一个调试模块(Debug Module, DM),且两个调试模块共同连接至同一个调试传输模块(Debug Transport Module, DTM),导致当时无论是开源 OpenOCD 还是商用调试器,均未支持此类“单DTM对接多DM”的结构。

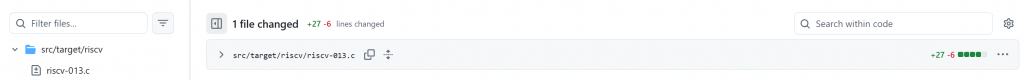

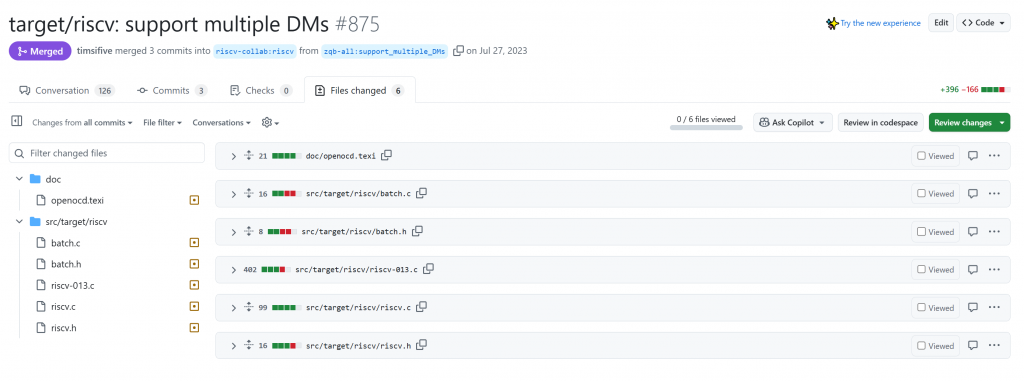

得益于 OpenOCD 的开源特性,团队得以对其进行自主修改。通过代码分析,发现可借鉴其他架构的现有配置,仅需 6 行代码即可实现对多 DM 调试结构的支持。完成修改并经 FPGA 验证后,进一步补充了调试日志等辅助内容,最终向上游社区提交了一个总计 27 行改动的初始 PR。

该 PR 获得了社区维护者的宝贵意见。经过 126 次评审讨论,最终完成修改并合入的 PR 代码行数扩充至 396 行。除增强检查机制、更新文档外,还对 DM 层接口进行了重构,使代码更加清晰、易于维护。

尽管最初未预料到仅6行的修改最终会演变为数百行的代码重构,但这一过程显著加深了团队对代码的理解,既降低了未来维护成本,同时为开源生态贡献了力量,是一次值得的投入。

在与社区的沟通中,开放、协作的氛围和有效的技术支持坚定了进迭时空将改进贡献回上游的决心——从最开始就把事情做对,而非在下游维护一个“打补丁”版本,反复应对版本冲突。

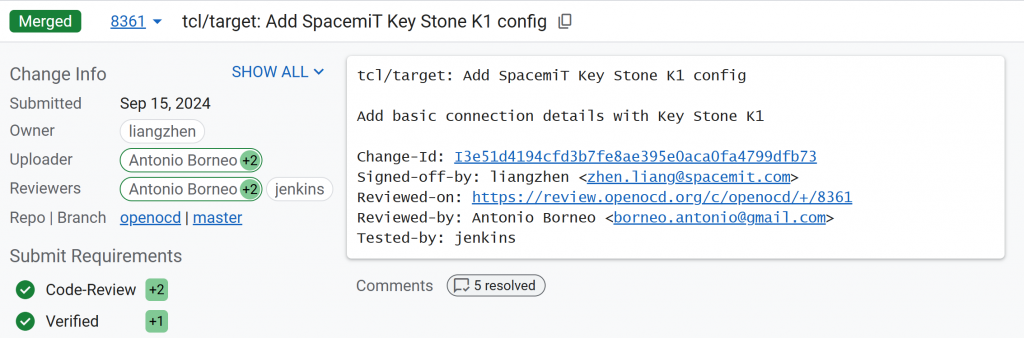

在 K1 调试支持完成后,相关配置文件已提交至 OpenOCD 主线。现在用户可直接使用上游版本调试 K1,无需额外补丁。

除了 K1 中发现和修复的若干问题,进迭时空在下一代芯片 K3 的研发过程中也识别出新的需求与挑战。例如,K3 采用的 X100 核心支持虚拟化扩展,其在调试虚拟机时暴露出 OpenOCD 地址转换逻辑的潜在问题;同时, Debug v1.0中 External Trigger 等新功能的引入,也催生了新的代码改进需求。在发现和解决这些问题后,进迭时空选择将其都提交至社区。等到 K3 正式交付,开发者将能够像使用K1时一样, 直接使用上游版本即可支撑调试需求,获得良好的调试体验。

截至目前,进迭时空已累计向 OpenOCD 与 riscv-tests 贡献并合入40余个Commit,另有数个补丁仍在评审中。在此特别感谢社区开发者,尤其是几位维护者(@timsifive、@en-sc、@JanMatCodasip)在代码评审与协作中给予的支持。

RISC-V 调试规范自 2018 年 12 月发布 v0.13 以来,经过社区共同努力,已于 2025 年 2 月正式批准 v1.0 版本。目前,riscv-openocd 的代码在持续完善,上游 OpenOCD 也正在加快合并来自 RISC-V Fork的改动。

随着 RISC-V 生态的发展,CPU 核心、SoC 系统与软件栈日趋复杂,高效可靠的调试手段愈发重要。RISC-V 本身的开放性与灵活性,也为调试技术的探索提供了广阔空间,例如日渐成熟的 Trace 规范即将带来更强大的调试能力。进迭时空将继续携手社区,积极参与 RISC-V 开源工具链的共建,共同推动 RISC-V 生态持续向前。